【CNMO科技】在东谈主工智能海潮席卷大家的配景下,半导体制造工艺的竞争已干预尖锐化阶段。手脚大家晶圆代工畛域的两大巨头金沙巴黎人娱乐城app官网,台积电与三星电子在先进制程门道上展现出天渊之别的策略取向:台积电全力激动"1纳米高妙化",而三星则聘任"2纳米踏实化"。这一策略分野不仅反馈了两家公司在工夫实力上的差距,更预示着将来大家半导体产业表情的深入变革。

台积电的"分岔式"策略:客户端与HPC端双线并进

2026年4月,台积电在北好意思工夫沟通会上精致公布了至2029年的先进制程门道图,其最引东谈主注主张变化是透顶颠覆传统的"一刀切"形式,转而接收"分岔式"策略。这一策略的中枢在于阐述不同市集需求,明确分离为两条并行的工夫赛谈。

芯片工场

客户端:每年迭代,强调成本与兼容性

针对智高东谈主机、耗费电子等客户端市集,台积电采用每年迭代的策略,重点在于成本铁心和IP复用:

N2U(2nm增强版):策划2028年量产,手脚N2平台的第三代蔓延版块,通过DTCO工夫达成同功耗下性能培植3%-4%,同频率下功耗缩小8%-10%

A13(1.3nm):策划2029年量产,手脚A14工艺的光学微缩版,线性尺寸缩小约3%,芯单方面积减少约6%,且与A14瞎想划定完全兼容

这种年度迭代形式确保了客户端产物的合手续竞争力,同期缩小了客户的移动成本。

AI/HPC端:每两年一代,追求性能极限

靠近AI和高性能计较需求的爆炸式增长,台积电特意设备了"高端线",不吝成本追求极致性能:

A16(1.6nm):原策划2026年下半年量产,现推迟至2027年。这是台积电首款接收后头供电收罗(Super Power Rail)工夫的工艺,基于第二代纳米片GAA晶体管,专为数据中心定制

A12(1.2nm):策划2029年量产,手脚A16的继任者,将接收第二代纳米片GAA晶体管和NanoFlex Pro工夫,不息缩小正反两面结构,达成举座密度培植

值得防范的是,台积电明确暗意,至少到2029年,所连络节点均不接收成本昂贵的High-NA EUV光刻成立,而是通过DTCO和架构优化挖掘现存EUV后劲。这一决议既体现了台积电对成本的选贤举能,也展现了其在工艺优化方面的深厚积存。

三星的策略转向:从激进到放心

与台积电的大呼大进造成明白对比,三星电子在先进制程门道上展现出昭着的策略收缩态势。

三星2纳米GAA工艺的量产良率当今看守在55%傍边,这一数字不仅逾期于台积电约10个百分点,更关节的是,它尚未达到眩惑高通等顶级无晶圆厂客户的最低门槛——后者对代工良率的条件频频不低于70%。

更令东谈主担忧的是,一朝后端封装经过完成纳入计较,三星的轮廓良率讨论将进一步下滑至40%傍边。这意味着每分娩十颗2纳米芯片,可能有六颗无法达到出货轨范。在晶圆代工行业,良率是决定成本和竞争力的中枢霸术,低良纯厚接导致单颗芯片成本飙升,松开了三星在价钱竞争中的上风。

三星芯片

三星已将其1.4纳米工艺的量产标的从原定的2027年推迟至2029年,这一调遣明晰地标明了其在激动更细巧制程上的严慎气派。比拟之下,台积电的A14工艺策划于2028年量产,时间上起初三星一年。

靠近工夫挑战,三星聘任将策略要点转向2纳米工艺的优化和平稳:

SF2P(2nm性能增强版):手脚第一代2纳米工艺(SF2)的迭代,策划2026年量产,在性能、功耗和面积上均有优化

SF2P+:手脚SF2P的光学收缩版块或第三代2纳米工艺,讨论在2027年至2028年间推出

这种"面面俱到"的策略天然在短期内难以缩小与台积电的工夫差距,但有助于三星在现存工艺基础上积存训戒,为将来的工夫冲突奠定基础。

市集表情:台积电的完全上风与三星的笨重解围

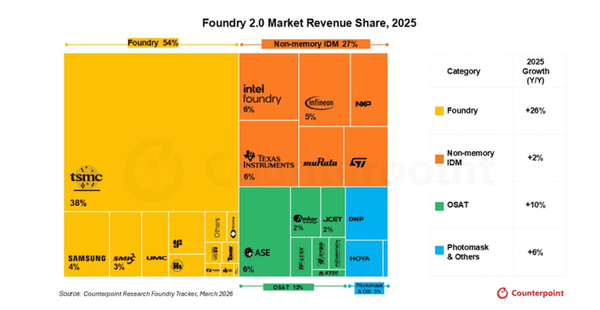

台积电和三星工夫门道的互异径直反馈在市集份额上。阐述Counterpoint Research的数据,2025年大家晶圆代工2.0市集范畴达到3200亿好意思元,同比增长16%。在这一市荟萃,台积电以38%的份额稳居第一,而三星的份额仅为4%。

台积电的客户结构呈现出昭着的"强人恒强"特征。苹果、NVIDIA、AMD、高通等大家顶级芯片瞎想公司齐是台积电的诚笃客户,这些客户不仅带来了踏实的订单,更通过恒久互助造成了深厚的工夫积存和生态壁垒。

图源收罗

以苹果为例,台积电将2纳米产能的60%径直打包卖给了苹果,这种深度绑定相干使得竞争敌手难以撬动。比拟之下,三星天然到手赢得了特斯拉AI6芯片的订单,但在高端客户争夺战中仍处于昭着时弊。

三星芯片代工业务在2025年赔本高达48.5亿好意思元,这一数字明晰地反馈了其在先进制程竞争中的窘境。天然讨论该业务将于2027年达成盈利,但在此之前,三星必须在工夫研发和成本铁心之间找到均衡点。

晶体管架构的代际跃迁

现时2纳米节点无数接收GAA(环绕栅极)纳米片晶体管,但1纳米节点需要更激进的架构。IMEC的门道图显现,从2纳米到A7(0.7纳米)节点将接收Forksheet(叉片)瞎想,随后在A5和A2节点引入CFET(互补场效应晶体管)。

三星已明确将在1纳米节点接收Forksheet结构,这是GAA纳米片的进化版,在轨范GAA基础上新增介质壁,可进一步培植晶体管密度与性能。台积电在1纳米制程中可能不会立即接收CFET,而是不息优化GAA架构。

光刻工夫的极限挑战

1纳米制程对光刻工夫建议了近乎暴虐的条件。ASML的High-NA EUV(0.55 NA)光刻机依然委派,其分辨率培植至8纳米线宽,表面上在双重曝光下可复旧1纳米芯片分娩。但每台成立成本朝上3.5亿欧元,重达15万公斤,需要250名工程师破耗6个月拼装。

台积电聘任暂不接收High-NA EUV的决议,既是对成本的考量,亦然对其工艺优化智商的自信。通过DTCO和架构改革,台积电试图在不依赖最先进光刻成立的情况下,达成性能和密度的合手续培植。

将来讨论:工夫、老本与耐烦的立体战役

1纳米制程的竞赛骨子上是一场"工夫、老本和耐烦"的立体战役。

台积电凭借其深厚的工夫积存、踏实的客户相干和严慎的成本铁心,不息在先进制程畛域保合手起初。其"分岔式"策略既满足了不同市集的需求,又确保了工夫发展的可合手续性。

三星则在资格工夫贫困后,聘任了一条更为放心的谈路。通过聚焦2纳米工艺的优化,三星试图在现存基础上积存训戒,为将来的工夫冲突奠定基础。天然这一策略在短期内难以缩小与台积电的差距,但有助于三星在强烈的市集竞争中保合手生计智商。

在这场竞赛中,产业链上游的中枢玩家一样饰演着关节变装。ASML手脚光刻机巨头,其High-NA EUV光刻机已成为1纳米工艺的入场券。而附近材料、泛林等成立制造商也在埃米级工艺的千里积、刻蚀等关节轨范见识着不行替代的作用。

1纳米是否会成为摩尔定律的尽头?或者在2030年,当第一派A10晶圆下线时,咱们才调找到谜底。但不错细则的是,这场"角逐1纳米"的战役金沙巴黎人娱乐城app官网,依然悄然打响,而台积电与三星的策略分野,将成为决定将来大家半导体产业表情的关节要素。